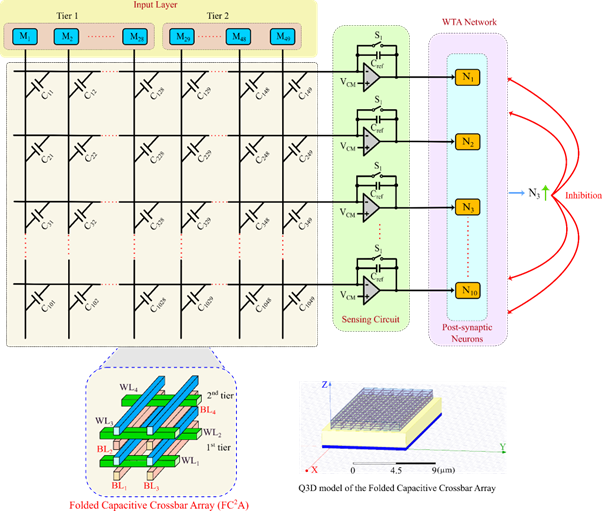

This project proposes a novel 3D folded capacitive synaptic crossbar array designed for in-memory computing architectures. In this architecture, the bit line is folded over the word line to enhance synaptic density. The scalability of the crossbar array is critical for performing complex computation tasks, as large-scale synaptic arrays are required to complete the operations. Therefore, the proposed folded capacitive crossbar array (FC2A) architecture decreases the word line interconnect length and physical crossbar area by 50%. Thus, it helps reduce crossbar-associated parasitics and optimize space utilization. Due to its higher synaptic density, the proposed architecture offers increased scalability for the crossbar array. Thus, the 3D folded capacitive crossbar can be used for designing systems with complex computational applications, eventually contributing to overall effectiveness.

Schematic of a brain-inspired computing system featuring a folded capacitive crossbar array (FC2A) shown with its Q3D model, connected to the sensing circuit through a winner-take-all (WTA) network.

The proposed folded capacitive synaptic crossbar is integrated into a brain-inspired computing system (BiCoS) designed for pattern recognition tasks using 65nm CMOS technology. The system uses a winner-take-all network (WTA), which prevents other neurons from firing. Analog in-memory computing architectures are prone to crossbar-associated parasitics. A Q3D model is developed for the proposed architecture to generate a circuit model incorporating all the crossbar-associated parasitics for accurate efficiency estimation. The designed parasitic model is adaptable and applicable to crossbars of any size. It allows exploration of parasitic effects on system performance at the schematic level without impacting post-layout simulation outcomes. This approach provides designers with a time-saving and efficient framework for system design.

Contributors: Sherin A Thomas, Devarshi Mrinal Das, and Rohit Sharma

Broad Field of Work: Microelectronics & VLSI

Faculty: Dr. Devarshi Mrinal Das, Prof. Rohit Sharma

Funding Agencies: ANRF

Year of Publication: 2024

Reference(s)

-

- S. A. Thomas, S. Kushwaha, R. Sharma, and D. M. Das, “Design and Analysis of 3D Integrated Folded Ferro-Capacitive Crossbar Array (FC2A) for Brain-Inspired Computing System,” IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS), vol. 14, no. 3, pp. 563-574, September 2024.

- S. A. Thomas, S. K. Vohra, S. Kushwaha, R. Sharma, and D. M. Das, “Modeling and Analysis of CMOS-based Folded Memristive Crossbar Array for 3D Neuromorphic Integrated Circuits,” 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, pp. 960-966, 2023.

Patent:

Indian Patent 565891, “3D FC2A: A 3D Integrated Folded Ferro-Capacitive Crossbar Array for Brain-Inspired Computing System”, S. A. Thomas, S. K. Vohra, R. Sharma, D. M. Das, Date of Grant: 01 May 2025.

Group Website (if available): https://devarshi.in/

Article: JETCAS article

Keywords:

In-memory computing

3D integrated circuit

Ferrocapacitive crossbar array

Neuromorphic computing

Interconnect