Our project titled rail-to-rail dynamic comparator (RRDC) presents the design and silicon validation of a suite of novel dynamic comparators targeting high-speed and energy-efficient analog-to-digital conversion. The proposed comparator architectures—CCDC (Cross-Coupled Dynamic Comparator), CC-RRDC (Cross-Coupled Rail-to-Rail Dynamic Comparator), and TS-RRDC (Three-Stage Rail-to-Rail Dynamic Comparator)—were fabricated in 180-nm CMOS technology and characterized. These designs address key challenges in comparator design such as rail-to-rail input common-mode voltage range, speed optimization, offset calibration, and kickback noise reduction.

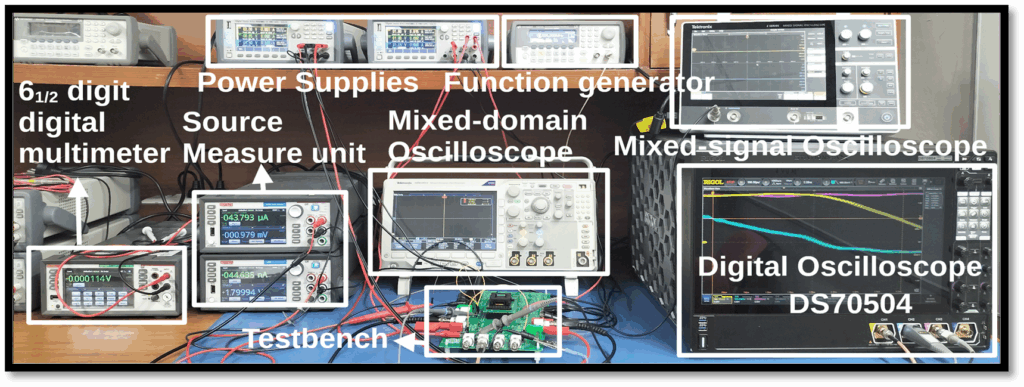

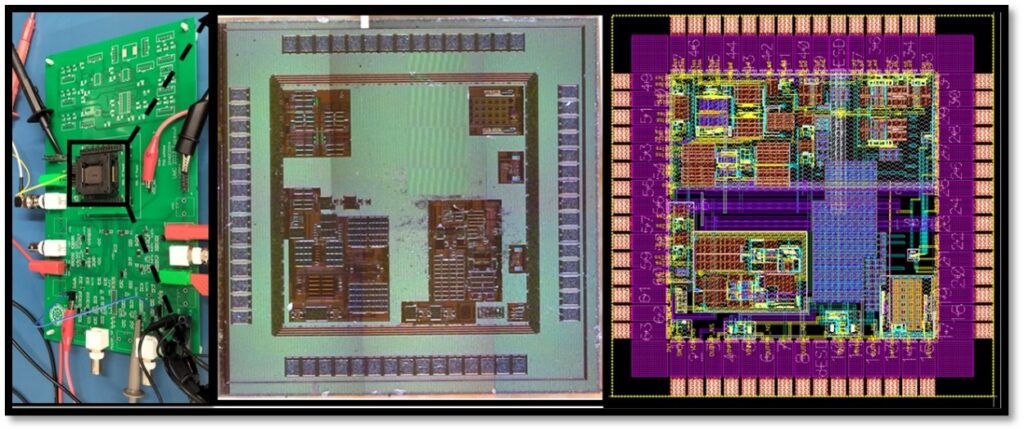

Testbench for characterization, Fabricated chip micrograph and layout in 180-nm CMOS process, integrating rail-to-rail dynamic comparators, low-noise amplifiers, EMI-immune OTAs, memristors, LIF neurons, and VCO circuits, developed by the ISDL team at IIT Ropar.

The first design, CCDC (Cross-Coupled Dynamic Comparator), introduces a cross-coupled preamplifier stage to enhance both differential and common-mode gain, which improves regeneration in the latch and leads to faster operation. Building on this, the CC-RRDC design merges NMOS and PMOS dynamic preamplifiers and selectively activates them based on the input common-mode level. This architecture supports true rail-to-rail input operation while maintaining energy efficiency and high speed. The novelty at the architectural level has been validated in an advanced technology node (28 nm) through rigorous post-layout simulations. The third design, TS-RRDC, features a modified three-stage structure that further improves kickback noise immunity—a major concern in high-speed analog front-ends—while preserving rail-to-rail common-mode performance.

All three designs target improvements in the core bottlenecks of comparator-based ADCs: speed, power, noise, and common-mode range. They offer practical paths for integration into low-power SAR ADCs, flash ADCs, and neuromorphic systems requiring fast, accurate signal comparison under varying input and supply conditions.

Date of the story: 28 July 2025

Author: Nidhi, Dr. Devarshi Mrinal Das

Broad Field of Work: Mixed signal IC Design

Faculty: Dr. Devarshi Mrinal Das

Funding Agencies: MeitY, ANRF

Acknowledgement: Rigol Technologies for providing the demo instrument no. DS70504 for delay characterisation.

Year of Publication: 2024, 2025

Reference(s):

-

- N. Sharma, S. A. Thomas, V. Hande and D. M. Das, “A Modified Three Stage Dynamic Comparator Achieving Rail-to-Rail Input Common-mode Range with <86 fJ.ns EDP,” in IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2025.3581335. (Link)

- N. Sharma, V. Hande, D. M. Das, “A Dynamic Comparator With Cross-Coupled Pre-Amplifier With <160 ps Delay and 81 fJ.ns EDP,” in Integrated Circuits and Systems, vol. 1, no. 4, pp. 206-213, Sept.-Oct. 2024, doi: 10.23919/ICS.2024.3505092. (Link)

- N. Sharma, Shivdeep, S. Vohra, V. Hande and D. M. Das, “A Rail-to-Rail Dynamic Comparator Featuring Complementary Cross-Coupled Pre-Amplifiers With <153 ps Delay and <77 fJ.ns EDP,” IEEE Transactions on Instruments and Measurement, 2025. (Under Review)

Group Website (if available): Nidhi, Devarshi Mrinal Das

Keywords:

Dynamic Comparator,

Rail-to-Rail,

ADC,

CMOS Fabrication,

Low Power