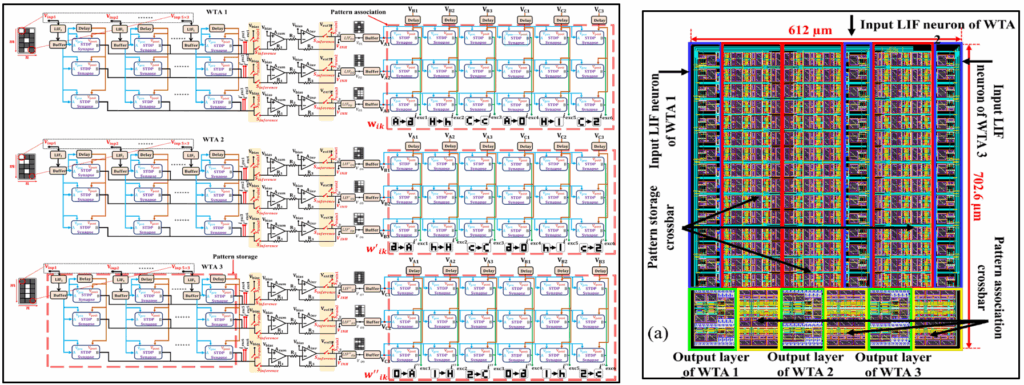

To enhance bioplausibility, sparsity, and information storage capacity in associative memory systems, we developed SpiMAM, a CMOS-based hardware prototype that, for the first time, demonstrates a fully on-chip trainable spiking multidirectional associative memory. SpiMAM supports complex associative functionalities, including one-to-one, one-to-many, and many-to-one associations. In contrast to ANN-based associative memories that rely on hardware-intensive training and digitally implemented weight storage and communication, SpiMAM adopts an analog computing paradigm. It integrating CMOS circuits that emulate memristor behaviour with spike-timing-dependent plasticity (STDP) learning and energy-efficient leaky integrate-and-fire (LIF) neurons. The information processing in the form of spikes and winner-take-all mechanism incorporated in SpiMAM helps to boost the bioplausability, sparsity, energy-efficiency and information storage capacity. The system is implemented at CMOS transistor level using 180nm standard CMOS technology, making it scalable, fabricable, and compatible with existing Indian foundry capabilities.

The proposed design demonstrates a significant reduction in hardware complexity by up to 86% in synapses and 70% in neurons compared to prior ANN-based approaches, while offering on-chip in-situ learning. The robustness of SpiMAM has been validated across process-voltage-temperature (PVT) variations, mismatch, memristor faults, and image noise. It shows high potential in multisensory integration, assistive technology, and robotic perception systems, where associations between diverse sensory modalities, such as vision, sound, and touch are critical. The work contributes toward scalable, silicon-compatible neuromorphic solutions for multisensory integration that bridge bio-inspired computing and real-world deployment.

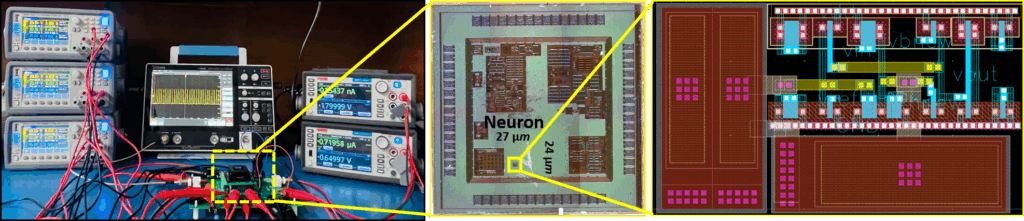

The team (research scholars in Microelectronics and VLSI design group) in IIT Ropar under the supervision of Dr. Devarshi Mrinal Das has successfully taped out its first IC fabricated in UMC 180 nm CMOS technology, containing multiple analog and mixed-signal circuits. The part of the chip area was contributed to a novel Leaky-integrate-and-Fire neuron (LIF) circuit. The designed neuron presents a simplified and area-compact LIF neuron designed in the subthreshold region for 0.6 V supply. The proposed neuron provides the adjustable refractory period, threshold control and lateral inhibitory mechanism with just 7 transistors and few femtofarad capacitors. The lateral inhibitory interface simplifies the inhibition process in the winner-take-all network (WTA) without any digital circuit overhead. This area- and energy-efficient LIF neuron with configurable features will help to bring large-scale integration of neurons for brain-inspired computing.

Date of the story: 26 July 2025

Contributors: Sahibia Kaur Vohra, Alex James, and Devarshi Mrinal Das

Broad Field of Work: IC Design for Neuromorphic Computing

Faculty/Students/Industry Personnel: Sahibia Kaur Vohra, Dr. Devarshi Mrinal Das, Dr. Mahendra Sakare, Prof. Alex James, Sahil Sharma, Nidhi Sharma, Shivdeep, Sherin Thomas

Funding Agencies: IIT Ropar (ISIRD) for test and characterisation instruments, ANRF-CRG for tapeout

Industry Engagement (if any): NA

Year of Publication: 2025

Reference(s):

- S. K. Vohra, M. Sakare, A. P. James, D. M. Das, “SpiMAM: CMOS Implementation of Bio inspired Spiking Multidirectional Associative Memory Featuring In-situ Learning”, in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 72, no. 1, pp. 2-13, Jan. 2025, doi: 10.1109/TCSI.2024.3427387.

- S. K. Vohra, S. A. Thomas, Shivdeep, M. Sakare and D. M. Das, “Full CMOS Circuit for Brain-Inspired Associative Memory With On-Chip Trainable Memristive STDP Synapse,” in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2023 doi: 10.1109/TVLSI.2023.3268173. (Among top 50 most popular papers of TVLSI from May 2023-Oct 2023, Dec 2023)

- S. K. Vohra, S. A. Thomas, M. Sakare and D. M. Das, “Circuit Implementatio of On-chip Trainable Spiking Neural Network using CMOS Based Memristive STDP Synapses and LIF Neurons,” in Integration, the VLSI Journal, March 2024, doi: 10.1016/j.vlsi.2023.102122.

Patent:

-

- Indian Patent Application No. 202411054405, “A neuron circuit and method of operation thereof”, S. K. Vohra, S. A. Thomas, M. S. Sakare, D. M. Das

Group Website (if available): Sahibia, Devarshi Mrinal Das

Keywords:

Associative memory

Spiking neural network

Spike-timing-dependent plasticity (STDP),

Multidirectional associative memory neural network (MAMNN)

CMOS circuits of synapses and LIF neurons.